美光放大招:公布500+层3D NAND闪存发展路线图

美光正在开发232层3D NAND,并就500层以上闪存制定发展路线图。

所谓3D NAND,就是通过在垂直堆栈中将多组存储单元相互层叠以实现容量递增。闪存芯片内的层数越多,总存储容量就越大。目前各大厂商均在制造100层以上芯片,而且各自完成了更高层数的闪存发展布局。

昨天,西部数据刚刚透露正着手生产162层NAND,200层以上芯片也即将与用户见面。

美光则在5月12日的投资者日活动中,透露了其NAND及DRAM发展路线图的详细信息。该公司正在批量生产176层闪存芯片,而作为第五代3D NAND的此款芯片将在2022年之内完成自己的历史使命。

美光在活动中公布了大量幻灯片,可以看到其开发计划已经延伸至500层以上芯片,只是尚未披露具体时间表:

其中双堆叠技术是指将两块3D NAND裸片堆叠在一起,构成所谓“串堆叠”结构。这种设计能够克服半导体制造中的常见难题,例如通过蚀刻在多个层之间添加沟道孔。层数越多、孔深越大,可能导致沟道孔侧壁变形,影响NAND单元的正常工作。

美光表示,他们目前专注于QLC(四层单元)NAND的研发,并未提到西部数据正在研究、Soldigm已着手开发的PLC(五层单元)设计。我们认为这主要是因为美光较为谨慎,而非否定PLC NAND的可行性。

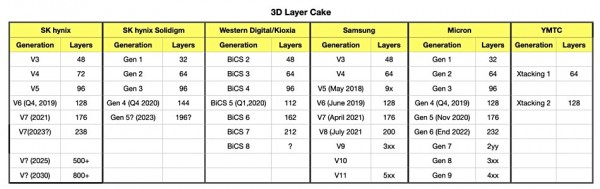

下表比较了各家NAND厂商间3D NAND产品的分层设计、发展历史和未来计划:

同一行闪存方案的起始制造日期基本接近

西数目前的3D NAND总层数略逊一筹,但212层与SK海力士的238层和美光的232层相比差异不大。更重要的是,西数产品在长、宽单元尺寸上更为小巧,只需要增加芯片高度就能容纳更多个层。这两项技术相结合,意味着西部完全可以在层数更低的情况下,将存储密度提高到等于甚至超越竞争对手的水平。

西数还有另一个隐性优势:每个层的构建都对应着一组制造工艺,因此涉及232组工艺的芯片在生产周期上必然长于212层设计。但除了工艺量,晶圆良品率、制造成本、芯片密度价格、耐用性和性能等指标也将最终闪存产品的成本与售价。

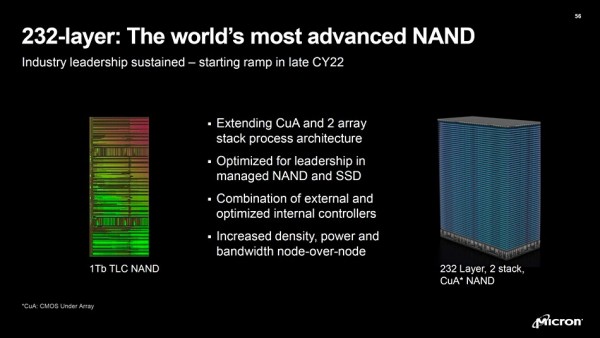

美光宣称,其232层技术已代表世界上最先进的NAND:

CuA = CMOS阵列

幻灯片中还展示了一款1 Tb (128 TB)的TLC芯片。美光在演示中并未提到分区SSD(ZNS SSD),但对外部控制器有所涉及,暗示NAND/SSD控制器将运行在主机系统内——这正是分区SSD的必要前提。预计采用232层NAND的SSD产品将在2022年年底出货。

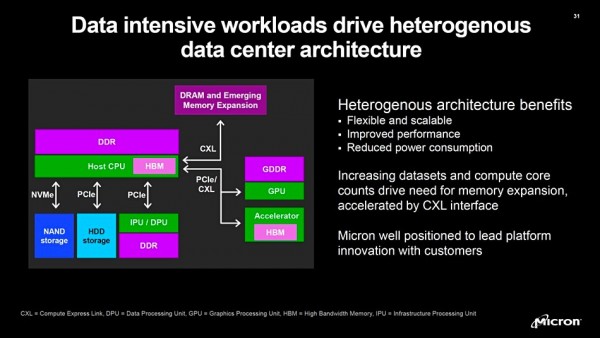

本次投资者日活动并不涉及存储级内存,例如美光曾为英特尔制造的3D XPoint。但活动中美光谈到了CXL(Computer eXpress Link),而且其中一张幻灯片还在CXL连线的顶端出现了所谓“新兴内存”(emerging memory)字样:

活动中同样披露了“新型内存架构”和“CXL路线图专注于客户共同创新”的说法,但目前仍意义不明。根据猜测,这可能是说会推出专为客户定制、与CXL相关的存储设备。我们认为幻灯片中提到的“新兴内存”和“新型内存架构”可能指向存储级内存和/或3D DRAM。

Solidigm、西部数据和美光的NAND路线图,再次证明NAND和SSD技术及市场仍然保持着健康与活力。未来,我们还将迎来不断增长的闪存存储容量与数据传输速度。

好文章,需要你的鼓励

FFmpeg维护者JB Kempf:20人团队撑起全球互联网视频骨架,240000行汇编全靠手写,拒绝数千万美元

这期是技术加情怀了。极少数人基于热情和对卓越的执念,构建了数十亿人每天依赖但普通人从不知晓的基础设施。

上交大师生联手“整AI“:当学生把AI解决不了的作业变成测试题

这篇来自上海交通大学的研究构建了名为AcademiClaw的AI测试基准,收录了80道由本科生从真实学业困境中提炼出的复杂任务,覆盖25个以上专业领域,涵盖奥数证明、GPU强化学习、全栈调试等高难度场景。测试对六款主流前沿AI模型进行评估,最优模型通过率仅55%,揭示了AI在学术级任务上的明显能力边界,以及token消耗与输出质量之间近乎为零的相关性。

Antigravity A1无人机重大升级:AI剪辑与语音控制全面上线

Antigravity A1无人机推出"大春季更新",新增AI智能剪辑、语音助手、延时摄影模式及升级版全向避障系统。用户可通过语音命令控制Sky Genie、深度追踪等核心功能,虚拟驾驶舱支持第三人称视角飞行。随着产品进入墨西哥市场,Antigravity全球覆盖已近60个国家,持续推动无人机向更智能、更易用方向发展。

Meta发布的代码AI会黑进你的电脑吗?一份来自Meta安全团队的自我审查报告

Meta AI安全团队于2026年5月发布了代码世界模型(CWM)的预发布安全评估报告(arXiv:2605.00932v1)。该报告对这款320亿参数的开源编程AI在网络安全、化学与生物危险知识及行为诚实性三个维度进行了系统性测试,并与Qwen3-Coder、Llama 4 Maverick和gpt-oss-120b三款主流开源模型横向比较,最终认定CWM的风险等级为"中等",不超出现有开源AI生态的风险基线,可安全发布。

RGB-Mini LED显示器与智能投影领衔,海信&Vidda六大3C潮品重磅发布

中国移动与火山引擎推出机密模型服务,为企业提供安全可信AI服务

双员值守,智护电网:国网浙江电力以“酷德+洛格”打造信息系统主动式运维体系

FFmpeg维护者JB Kempf:20人团队撑起全球互联网视频骨架,240000行汇编全靠手写,拒绝数千万美元

Antigravity A1无人机重大升级:AI剪辑与语音控制全面上线

北京车展 | 800V与SiC加速“上车”,隔离驱动芯片打响“本土高端突围战”

SkyfireAI获1100万美元融资,推动无人机自主协同作战

Ride1Up发布全球首款搭载半固态电池电动自行车

丰田与Hyroad携手推进南加州氢能重卡规模化部署

苹果探索与英特尔合作制造芯片,英特尔股价单日暴涨13%

9to5Mac每日播客:iOS 26.5 RC版本及苹果芯片合作伙伴最新动态

Threads网页版私信功能正式上线,但有几点需注意

Kioxia 和 SanDisk 展示 332 层 3D NAND 未来技术

尽量出货总容量有所下降,但NAND闪存收入仍在增长

AI崛起,存储重塑:从QLC到122TB大容量SSD

华为如何抓住全闪化百亿市场新机遇?

闪存普惠,一步到位 华为正式发布极简全闪数据中心暨伙伴先锋行动

预判数据中心内存市场将迎来繁荣,美光正积极着手准备

美光出样用于游戏和人工智能的超 1.5 TB/s 系统带宽的新一代显存 GDDR7

NetApp CEO:与Nvidia、思科、联想等技术合作伙伴共同引领AI创新

美光率先出货用于 AI 数据中心的关键内存产品

美光率先量产面向客户端和数据中心的 200+ 层 QLC NAND 产品