研究人员设计出比DDR5快30倍的3D DRAM

东京工业大学的科学家们设计出一种新型3D DRAM栈,其顶部配有处理器,可提供比高带宽内存(HBM)高出四倍的传输带宽与仅五分之一的访问功耗。

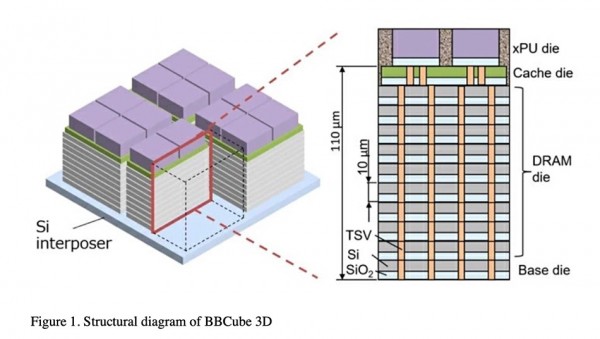

HBM通过中介层将小型DRAM栈接入至CPU,从而避开了受到CPU限制的DRAM插槽数量。在Bumpless Build Cube 3D(简称BBCube3D)概念中,单个DRAM芯片通过微凸块(连接器)与上方或下方的芯片相连,而连接孔(通过硅通孔,即TSV)穿过芯片将各个微凸块连接起来。

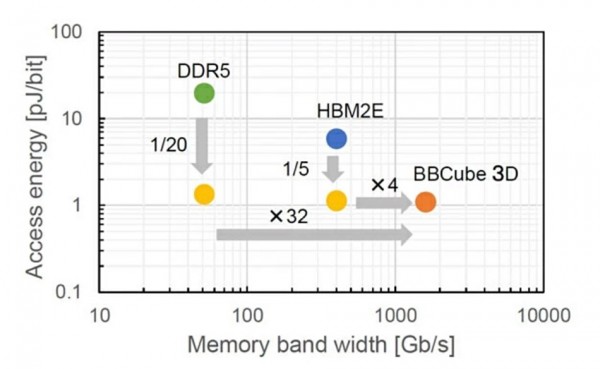

研究团队负责人Takayuki Ohba教授表示,“BBCVube 3D拥有良好的性能潜力,可实现每秒1.6 TB理论传输带宽,相当于DDR5的30倍、HBM2E的4倍。”

研究人员们削薄了每个DRAM芯片,同时消除了BBCube3D晶圆叠层(WOW)设计中的微凸块。与DDR5或HBM2E(第二代高带宽扩展内存)设计相比,这种新方案使得内存块拥有更高速度和更低的运行能耗。这是因为前者的运行温度更高,而且凸块的存在会增加电阻/电容和延迟。

HBM微凸块还会占用空间,且芯片的硬度也必须达标,否则无法承受堆叠层合并所带来的压力。通过消除微凸块,每个内存芯片都可以变得更薄、硅通孔更短,从而实现带好的散热效果。BBCube3D设计还不需要中介层,因为处理单元、CPU或GPU能够直接绑定至缓存芯片,而缓存芯片本身又可绑定至DRAM栈的顶端。

研究人员们解释道,“更短的硅通孔互连能够为CPU和GPU等高温设备提供更好的散热……高密度硅通孔本身就可以充当热管,因此即使是在3D结构当中,其预期运行温度也会更低。”

“由于硅通孔长度更短且信号并行度更高”,BBCube“能够实现更高带宽与更低运行功耗”。

通过调整相邻IO线的时序来确保其彼此异相,研究人员还成功减少了分层DRAM中的串扰。这种方法被称为四相屏蔽输入/输出,意味着IO线永远不会与其紧邻的线路同时发生值变化。

下图所示,为BBCube与DDR5和HBM2E内存技术的速度与能耗比较。可以看到,其带宽达到DDR5内存的32倍,速度相当于HBM2E的4倍。与此同时,BBCube 3D设计还实现了比DDR5和HBM2E更低的访问能耗水平。

Ohba解释道,“由于BBCube的热阻和阻抗都更低,所以能够缓解3D集成设计中经常出现的热管理和电源问题。此次提出的新技术能够在达成可观传输带宽的同时,将每bit访问功耗降低至DDR5的二十分之一和HBM2E的五分之一。”

BBCube 3D属于高校主导的研究项目。关于该项目的详细背景信息,可以在MDPI Electronics论文《论使用晶圆上晶圆(WoW)与晶圆上晶片(CoW)实现兆级三维集成(3DI)的BBCube》(https://www.mdpi.com/2079-9292/11/2/236)中找到。论文提到,“BBCube允许将堆叠的芯片数量提升至HBM的4倍,意味着使用16 Gb DRAM裸片时内存容量可以达到64 GB。”

文章同时指出,“通过堆叠40层DRAM,即可实现Tb级别的3D内存。”

论文《Bumpless Build Cube (BBCube) 3D:使用WoW与CoW的异相3D集成实现TB/s级传输带宽与最低bit访问功耗》(Bumpless Build Cube (BBCube) 3D: Heterogeneous 3D Integration Using WoW and CoW to Provide TB/s Bandwidth with Lowest Bit Access Energy)对BBCube 3D概念也做了描述,文章发表于2023年6月的IEEE 2023 VLSI技术与电路研讨会。

好文章,需要你的鼓励

Coursera推出AI面试官帮用户练习求职面试

Coursera在2025年连接大会上宣布多项AI功能更新。10月将推出角色扮演功能,通过AI人物帮助学生练习面试技巧并获得实时反馈。新增AI评分系统可即时批改代码、论文和视频作业。同时引入完整性检查和监考系统,通过锁定浏览器和真实性验证打击作弊行为,据称可减少95%的不当行为。此外,AI课程构建器将扩展至所有合作伙伴,帮助教育者快速设计课程。

如何让AI像电影配乐师一样创作完整的长篇音频故事——腾讯ARC实验室团队AudioStory突破性进展

腾讯ARC实验室推出AudioStory系统,首次实现AI根据复杂指令创作完整长篇音频故事。该系统结合大语言模型的叙事推理能力与音频生成技术,通过交错式推理生成、解耦桥接机制和渐进式训练,能够将复杂指令分解为连续音频场景并保持整体连贯性。在AudioStory-10K基准测试中表现优异,为AI音频创作开辟新方向。

英国政府研究显示:AI技术或在辅助功能领域实现最大突破

英国政府研究显示,神经多样性员工从AI聊天机器人中获得的收益远超普通同事。在Microsoft 365 Copilot试点中,神经多样性员工满意度达90%置信水平,推荐度达95%置信水平,均显著高于其他用户。患有ADHD和阅读障碍的员工表示AI工具为他们提供了前所未有的工作支持,特别是在报告撰写方面。研究表明,AI工具正在填补传统无障碍技术未能解决的职场差距,为残障人士提供了隐形的工作辅助。

Meta与特拉维夫大学联手打造VideoJAM:让AI生成的视频动起来不再是奢望

Meta与特拉维夫大学联合研发的VideoJAM技术,通过让AI同时学习外观和运动信息,显著解决了当前视频生成模型中动作不连贯、违反物理定律的核心问题。该技术仅需添加两个线性层就能大幅提升运动质量,在多项测试中超越包括Sora在内的商业模型,为AI视频生成的实用化应用奠定了重要基础。

英特尔宣布领导层任命,强化客户端、数据中心和代工业务

Coursera推出AI面试官帮用户练习求职面试

英国政府研究显示:AI技术或在辅助功能领域实现最大突破

Gemini应用程序终于扩展至音频文件支持

Firefox推出iPhone"摇动即可总结"功能

苹果发布iPhone 17系列、Watch 11和新款AirPods Pro 3

IBM构建的AI落地新路径,从烟台启程

腾讯混元发布并开源图像模型2.1,支持原生2K生图

联想联合伊利重构乳业价值链,“AI+”出无限可能

法国AI独角兽Mistral获ASML领投20亿美元融资

VAST Data收购Red Stapler加速超大规模云服务布局

Claude新文件创建功能存在深层安全风险