3D NAND为实现四级单元提供了可行性

关于四级单元闪存纠错问题的潜在解决方法。

与此前的平面NAND相比,3D NAND技术的运用将使得错误检查代码更易于实现,这也进一步确定了容量提升的四级单元技术的可行性。

错误检查代码(ECC)技术的使用范围包括通过采用算法以计算为存储数据添加冗余所需添加与使用的位数,在固定大小区域内工作的分组代码与Reed-Solomon编码即是此类技术的应用实例。并且与该技术能够完成的纠错量相比,其可检测到的错误数量更多。

低密度奇偶校验(LDPC)编码是ECC技术的一种较新版本。BCH(Bose-Chaudhuri-Hocquenghem)编码则是另一项纠错技术,这种二进制BCH编码可被设计用于多位数纠错。通常而言,客户希望能够完成的纠错位数越多,则需要添加到数据中的冗余ECC位数就越多。

由于读取单元无法提供明确的1或0,因此在这种情况下,一个或多个字节的值可能会因错误而失真,所以NAND闪存需要配有ECC。

而ECC编码则能够检测并纠正以上所提及的错误。

随着NAND读取难度的增加,需要添加的ECC位数与ECC算法的复杂程度也随之提高。其中,“读取难度”一种概括性说法,其具体是指单元可读性随着单元尺寸与其所存储的位数增加而降低。

举例而言,小单元之间可能存在跨区效应,具体表现为一个单元内的设置值可能会对相邻单元内的设置造成一定影响。而其中所涉及的设置值还包括电子——其数量与稳定性会随着单元尺寸缩小而降低。

因此,与SLC(一级单元)相比,MLC(二级单元)与TLC(三级单元)闪存的读取固然会更困难。当然,尽管QLC(四级单元)在技术上已具有一定可行性,但由于单元可读性以及ECC编码与算法仍是亟待解决的两大难题,所以直到现在QLC还尚未具备实用性。

SanDisk公司曾于2009年试图采用43纳米几何平面结构实现QLC NAND的生产,但在经历了一年左右的研究后即选择了放弃。

同样,与25纳米单元以及35纳米单元相比,20纳米的MLC闪存单元更难实现读取。此外,16纳米的MLC闪存单元则是很难实现再次读取,而在此级别上所采用的ECC已经实现了BCH与LDPC ECC技术的融合。

根据Objective Analysis公司的Jim Handy简要报告可知,选择采用3D NAND将会让这些难题简化。

其中的两大主要原因如下:

首先,当3D NAND闪存芯片建成之后,单元尺寸将从15纳米恢复至40纳米左右,尔后即可在该芯片上采用最先进的2D或平面NAND技术。

其次则是源于3D NAND的构建方式。“3D NAND的浮栅或电荷捕获将在作为通道的接杆附近形成一个圆圈,从而让其面积增加了三倍以上。故而现在3D NAND芯片的面积大致相当于一款90纳米的平面NAND芯片。”

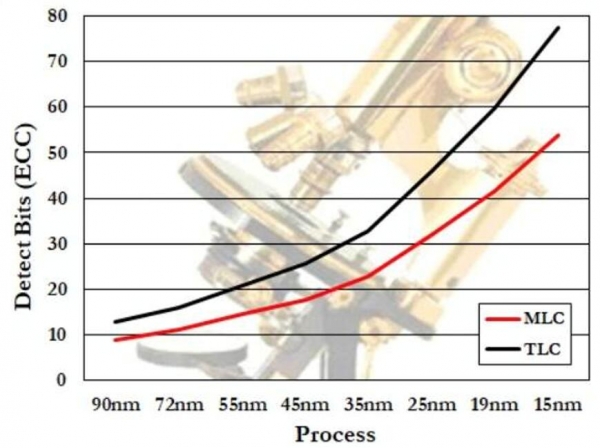

另外,Jim Handy还提供了一张图表以展示MLC与TLC闪存在不同单元尺寸条件下通常所需的ECC位数。

根据图表显示,TLC NAND闪存的单元尺寸在15纳米工艺几何尺寸时所需ECC位数已超过75比特,而当芯片的几何尺寸为90纳米时,ECC的位数需求则在15以下。

对此,Handy在其报告中写道:“我们据此即可推断QLC 3D NAND所需的位数将少于20。这也是为何与以往的平面NAND相比,采用3D NAND能够提升QLC可行性的原因。”

此外,Handy还描绘了每单元拥有更多位数的前景。“从长远看来,我认为大多数3D NAND控制器将会采用LDPC以确保每单元存储4字节以上的数据。当然,实现这一目标需要一些时间。而在短期内,3D NAND将能够通过使用简单的BCH算法完成其向QLC转变。”

试想每单元能够存储5比特字节的闪存——或称之为五级单元或PLC闪存?由于QLC已经用于代表四级单元闪存,所以我们不能将五级单元按quintuple level cell首字母缩写命名,并且其将比QLC闪存增加25%,每单元存储为5比特而非4比特。因此,一款容量为1 TB的QLC SSD或将可能变为1.25 TB的PLC SSD。恩,此番前景的确令人欣喜,但或许仍需数年才能得以实现。

目前看来,QLC闪存似乎已具备一定的可行性,我们或将于今年年底便可见其真身。

好文章,需要你的鼓励

我们希望AI有多智能?世界模型可能比我们更懂世界

近年来,AI学会了写作、生成图像、创建视频甚至编写代码。随着这些能力成为主流,研究重点转向更深层问题:机器能否真正理解世界运作方式?世界模型应运而生,从1950年代概念到2024年OpenAI的Sora、2025年英伟达Cosmos等突破性应用。与语言模型基于文本预测不同,世界模型专注预测环境变化,通过学习因果关系实现推理规划。在机器人、自动驾驶等物理AI领域前景广阔,但面临计算资源需求高、数据收集困难等挑战。

当大模型遇见古希腊逻辑学:印度统计学院团队揭示AI推理的“双重人格“

印度统计学院研究团队对14个大语言模型进行三段论推理测试,发现AI存在"双重人格"现象:顶级模型在逻辑推理上近乎完美(99.6%),但常识判断仅达随机水平(52%)。研究揭示了AI与人类推理的根本差异——AI正成为纯逻辑机器,而非具备常识的智能体,为AI发展方向提出深层思考。

首席信息官角色将在2026年扩展的四种方式

CIO角色正经历前所未有的转型。技术领导者不再仅专注于数字化转型和云迁移,还将承担企业可持续发展、AI治理和战略平台整合等责任。AI将从部署工具转变为重塑企业对技术领导者期望的核心力量。2026年CIO将承担负责任AI治理、推动AI驱动的平台整合、从IT转向企业级创新,以及成为可持续发展的首要管理者四大新职能。

北京大学团队打造数据准备“流水线“:让AI训练数据制作如同烹饪大餐般标准化

DataFlow是北京大学等机构开发的AI数据准备统一框架,通过近200个可复用算子和智能助手DataFlow-Agent,将传统手工数据处理升级为标准化流水线。实验证明其数据质量显著提升模型性能,在数学推理、代码生成、数据库查询等任务中均取得突破性改进,仅1万样本效果可媲美百万级传统数据集。

我们希望AI有多智能?世界模型可能比我们更懂世界

首席信息官角色将在2026年扩展的四种方式

Waymo正在测试Gemini在无人驾驶出租车中的车载AI助手功能

数据中心从幕后走向台前的转折之年

意大利要求Meta暂停禁止竞争对手AI聊天机器人使用WhatsApp的政策

让老旧Windows和macOS系统延续生命力

微软计划到2030年用Rust语言替换所有C和C++代码

2026年创客工具迎来重大升级,这些新技术值得期待

2025年十大网络故事盘点

UNIX V4磁带成功恢复:首个C语言编写的UNIX版本重新运行

AWS为Nutanix AHV虚拟化平台新增混合云存储支持

MiniMax发布M2.1大语言模型,大幅提升多语言编程能力